|

|

|

|

|

| |

|

제 목 :

[인텔] R-타일 내장 애질렉스 7 FPGA 출시

[인텔] R-타일 내장 애질렉스 7 FPGA 출시 |

|

작성자 :

|

등록일 : 2023-05-25 오전 11:36:11 |

|

|

|

|

|

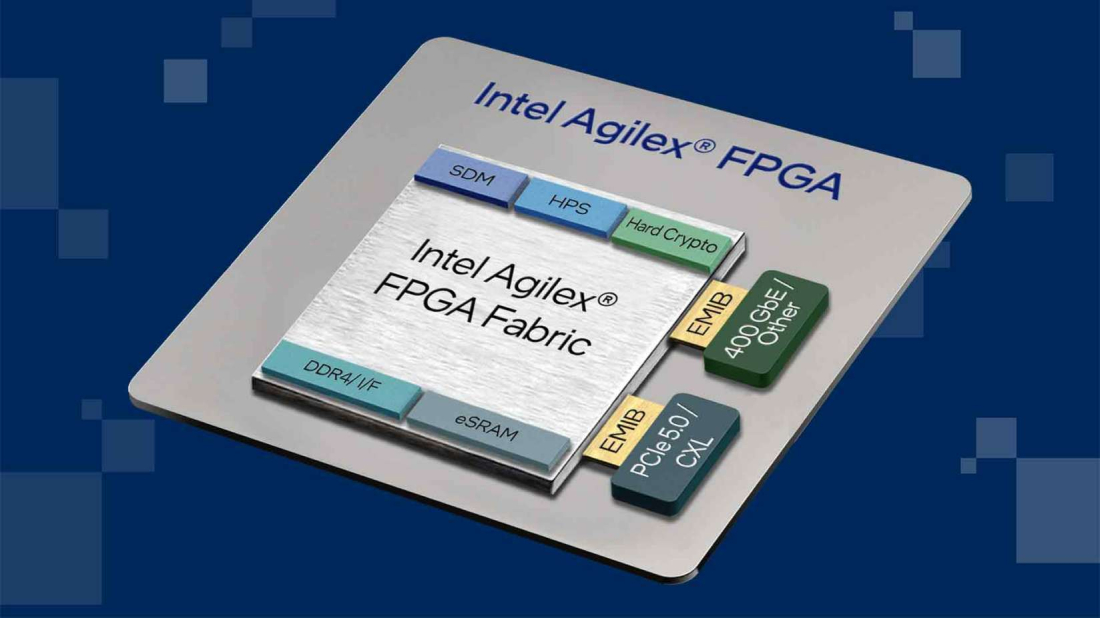

인텔 프로그래머블 솔루션 그룹은 R-타일이 내장된 인텔 애질렉스® 7(Intel Agilex® 7)을 양산 및 출하한다고 25일 밝혔다. 애질렉스 7은 FPGA 최초로 PCIe 5.0 및 컴퓨트 익스프레스 링크(CXL) 기능과 해당 인터페이스를 지원하는 하드IP(Hard IP)를 제공한다.

샤논 폴린(Shannon Poulin) 인텔 부사장 겸 프로그래머블 솔루션 그룹 총괄은 “고객은 현재 워크로드를 효율적으로 관리할 뿐만 아니라 필요에 따라 기능을 전환하는 데 필요한 확장성과 개별성을 제공하는 최첨단 기술을 요구하고 있다”며 “애질렉스 제품은 고객이 필요로 하는 속도, 성능, 기능을 갖춘 프로그래밍 가능한 혁신을 제공하는 동시에 미래를 위한 유연성과 회복탄력성을 제공한다. 일례로, 고객들은 PCIe 5.0 및 CXL를 지원하는 R-타일을 활용해 소프트웨어 및 데이터 분석을 가속화함으로써 몇 시간이 소요되는 처리 시간을 단 몇 분으로 단축하고 있다”고 말했다.

|

|

|

|

| 덧글쓰기 |

|

|

|

|

|

|

|

|

|

|

|